Lasers in Manufacturing Conference 2021

# Excimer laser annealing with a controlled grain size of poly-Si films for large display panels

Mizutani Akira<sup>a</sup>, Hamano Fuminobu<sup>b</sup>, Nakamura Daisuke<sup>b</sup>, Goto Tetsuya<sup>c</sup>, SitiRahmah Aid<sup>d</sup>, Ikenoue Hiroshi<sup>a,b,\*</sup>

<sup>o</sup>Department of Gigaphoton Next GLP, Kyushu University <sup>b</sup>Graduate School of Information Science and Electrical Engineering, Kyushu University <sup>c</sup>New Industry Creation Hatchery Center, Tohoku University <sup>d</sup>Malaysia-Japan International Institute of Technology, Universiti Teknologi Malaysia

#### Abstract

Low-temperature polycrystalline Si (LTPS) thin-film transistors crystallized by excimer laser annealing (ELA) have been used as backplanes for active-matrix organic displays owning to their high mobility. However, the current ELA method requires a line beam with the major axis dimension equivalent to the minor axis of the substrate size, whereby limiting its applicability to large glass substrates. One solution to this problem is to anneal the entire surface of the substrate by folding back the beam; this process is referred to as the multi-scan annealing. However, in the overlapping region caused by the multi-scan annealing, the grain size increases, resulting in uneven device characteristics on the glass substrate. In this study, we annealed amorphous silicon by folding back the beam with an intensity distribution to observe the morphologies of grains in single and double scan region and to evaluate the mobility of the TFTs. As a result, it was demonstrated that uniform size grains could be formed in the single and double scan region, and that the dependence of mobility on the number of laser shots was low. In addition, the amount of change in mobility due to the presence of scan borders in TFT channel was clarified and it was shown that this can be attributed to misalignment of the stage.

Keywords: LTPS; TFT; laser annealing

### 1. Introduction

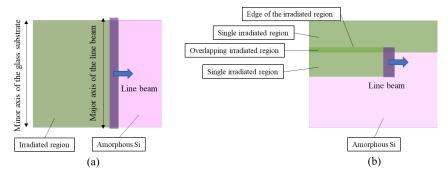

Low-temperature polycrystalline Si (LTPS) thin-film transistors (TFTs) crystallized by excimer laser annealing (ELA) are expected to be useful as backplanes for large active-matrix organic displays owing to their high mobility in comparison with that of amorphous Si (a-Si) and oxide semiconductor transistors. In the flat-beam ELA used in industry, grains of about 300 nm are formed by scanning a line beam only once on a glass substrate. However, this ELA method requires the major axis dimension of the line beam to be equivalent to the minor axis of the substrate size, which limits the size of the glass substrate. To solve this problem, it is necessary to anneal the entire surface of the substrate by folding the beam; this process is referred to as the multi-scan annealing as illustrated in Figure 1. In the double scan region caused by multi-scan annealing, the grain size increases, resulting in uneven device characteristics [1][2][3]. To address this issue, based on the dependence of grain size on the fluence in flat-beam ELA [4], Kim et al. clarified the fluence at which the grain size is equivalent for both single and double scans (approximately 230 mJ/cm² for a-Si with a film thickness of 100 ± 20 nm). [1][2]. However, the mobility of the TFT fabricated using this method is only 0.15 cm² V-¹ s-¹, owing to the small grain size of 4 nm [2], which is much less than

<sup>\*</sup> Corresponding author. Tel.:+81 92-802-3774. E-mail address: ikenoue.hiroshi.834@m.kyushu-u.ac.jp.

the grain size of industrial applications (~300 nm). In contrast, studies have been conducted on controlling the grain size using a mask-like laser beam [5] and a substrate embedded seed [6].

To the best of our knowledge, no studies have attempted to reduce the increase in the grain size in the double scan region by using the beam with intensity distribution. Therefore, in this study, we attempted to control the grain size through laser annealing with an intensity distribution to reduce the increase in grain size in the single and double scan region during multiscan annealing. We also evaluated the change in grain size at the border region during irradiation and the resulting change in the TFT characteristics.

Fig. 1. (a) Single scan annealing and (b) multi-scan annealing

# 2. Experimental procedures

## 2.1. Laser annealing system

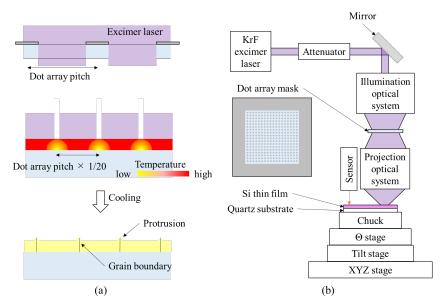

The laser annealing system has been described previously [7]. In this study, annealing of a-Si was annealed using a laser beam with an intensity distribution. As depicted in Figure 2 (a), crystal growth starts around the lower-intensity parts of the intensity distribution and square grains are formed. Therefore, a laser beam with a periodic intensity distribution can form uniform square grains with a length of 2  $\mu$ m. The intensity distribution was generated by projecting intensity distribution after dot array mask to the sample surface with a reduction rate of 1/20. The mask comprised of circular metal thin films with a diameter of 20  $\mu$ m at a 40  $\mu$ m pitch grid position to block the irradiated laser beam. Figure 2 (b) illustrates a schematic of the laser-annealing system. An excimer laser [GT600K/ Gigaphoton Inc., wavelength: 248 nm, pulse duration (full width at half-maximum) of 80 ns) was used as the light source. The dot array mask was illuminated by laser from the illumination optical system, which equalizes the illuminance. The projection optical system projected light from the dot array mask onto a 200  $\mu$ m × 200  $\mu$ m area on the sample surface. Before annealing, the focus was adjusted using a sensor to measure the

Fig. 2. Adapted from reference [7]. (a) Concept of laser annealing with an intensity distribution using a dot array mask. (b) Schematic of excimer laser annealing setup.

length of the laser. The fluence of the laser was approximately 660 mJ/cm<sup>2</sup> and the repetition rate of the laser was 10 Hz. The scan speed was set to 0.2 mm/s to align the intensity distribution with the formed grains.

### 2.2. TFT fabrication

TFT fabrication was performed as described previously [7]. First, a-Si (100 nm) films were deposited onto a quartz substrate. Subsequently, the a-Si film was crystallized using ELA. After poly-crystallization of the Si film, the poly-Si film was formed by creating island patterns using photolithography and wet etching. A gate-insulator  $SiO_2$  (100 nm) film was deposited at 350 °C. The gate electrode was fabricated by depositing a TiN (150 nm) film and patterned by wet etching. P+ ions at 140 keV with a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> were implanted to form a self-aligned source/drain region utilizing the gate electrode pattern as a mask. This was followed by activation annealing in an  $N_2$  atmosphere at 550 °C for 1 h. Next, a dielectric film of  $SiO_2$  (150 nm) was deposited. The contact holes were opened using wet etching. A metallic contact of Al was deposited and patterned by wet etching. Finally, the TFT was annealed at 400 °C for 0.5 h under the forming gas (Ar/H<sub>2</sub> = 900/100 sccm). In this study, the length (*L*) and width (*W*) of the fabricated TFT channels were 20 and 30 µm, respectively.

# 2.3. Measurement of TFT characteristics

The morphology of the poly Si was evaluated by SEM observation after Secco etching. The drain current ( $I_D$ )—gate voltage ( $V_D$ ) characteristics of the fabricated TFTs were measured at room temperature (approximately 300 K) using a Keysight B1500A semiconductor device analyzer. The TFT field-effect mobility ( $\mu_{FE}$ ) was calculated using the following equation:

$$\mu = \frac{L}{W} \frac{1}{C_{OX} V_D} \frac{\partial I_D}{\partial V_G} \tag{1}$$

, where  $C_{OX}$  denotes the gate oxide capacitance per unit area,  $I_D$  denotes the drain current,  $V_D$  denotes the drain bias, and  $V_G$  denotes the gate bias.

#### 3. Results and discussion

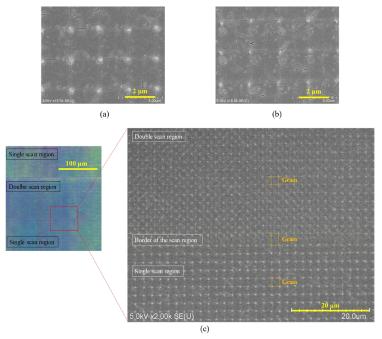

We first performed multi-scan annealing of the laser with the intensity distribution and compared the grain morphologies to determine the grain sizes in single and double scan regions. Figure 3 illustrates the morphology of the single scan (10 pulses/point), double scan (20 pulses/point) and border region. Figure 3 (a) and (b) illustrates that squares with dimensions

Fig. 3. (a) Single scan region, (b) double scan region, and (c) Morphology of each region

of 2  $\mu$ m x 2  $\mu$ m were formed in the single and double scan region. This is not attributed to the difference in the number of shots, but the grain size and position are determined according to the intensity distribution. In comparison with flat beam annealing, where a grain size was differ by approximately two times between signal and double scan region [2], in this method the difference of the grain size was well decreased. The optical microscope image in Figure 3 (c) shows that there are small mura in the single scan and double scan regions. The horizontal direction mura corresponded to the border of the scan. The vertical direction mura corresponded to the border between pulses. Rectangles with dimensions of 2  $\mu$ m x 3  $\mu$ m were formed at the border due to the misalignment of the stage by 1  $\mu$ m.

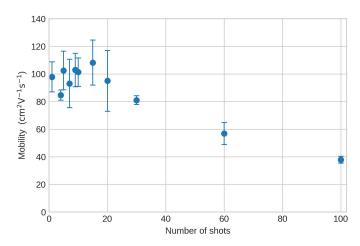

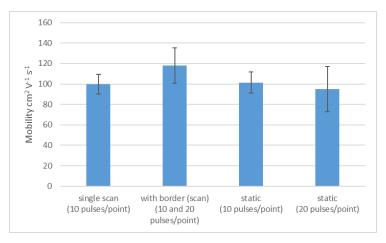

Next, we annealed a-Si by static exposure to investigate the change in TFT characteristics with the number of shots and investigated the relationship between the mobility of TFT devices and the number of shots. Table 1 and Figure 4 show the relationship between the number of annealing shots and the evaluation results of the mobility of the TFT devices. As shown in Table 1, for approximately 20 shots or less, the change of mobility with respect to the number of shots was less than 7%, which was the standard deviation calculated from the mean value of mobility of the TFTs fabricated at each pulse number. The mobility value was approximately 100 cm² V-¹ s-¹, which was sufficient for industrial use. The low shot number dependence of the mobility can be attributed to the fact that the mobility depends mainly on the grain size [10]. The variation in mobility was due to grain disorder caused by the focus shift during laser annealing, non-uniformity of film thickness during the device fabrication process, and randomness of grain orientation. The first two problems could be solved through industrialization. The number of shots dependence of the mobility was low less than 20 shots but as shown in Figure 4, a decrease in mobility occurs as exceed than 20 shots. The reason for this was that the polysilicon film was damaged by the laser. Therefore, it was suggested that the number of laser irradiation should be 20 pulses/point in this method.

Table 1 Mobilities of fabricated TFTs annealed by different numbers of shots.

| Number of shots                                                                                       | 1     | 4     | 5     | 7        | 9     | 10    | 15    | 20    |

|-------------------------------------------------------------------------------------------------------|-------|-------|-------|----------|-------|-------|-------|-------|

| Average of mobility of TFTs                                                                           |       |       |       |          |       |       |       |       |

| annealed by different numbers of                                                                      | 97.8  | 84.7  | 102.6 | 93.2     | 102.9 | 101.3 | 108.2 | 95.0  |

| shots.<br>(cm² V <sup>-1</sup> s <sup>-1</sup> )                                                      | (N=2) | (N=4) | (N=9) | (N=4)    | (N=7) | (N=8) | (N=6) | (N=6) |

| Standard deviation of mobility of<br>TFTs annealed by different<br>numbers of shots.<br>(cm² V-1 s-1) | 10.9  | 3.7   | 14.0  | 17.6     | 12.1  | 10.3  | 16.4  | 22.0  |

| Average and standard deviation of mobility above. $(cm^2 V^{-1} s^{-1})$                              |       |       |       | 98.2±7.3 |       |       |       |       |

When multiple scans were performed, borders were created by the scans, as depicted in Figure 3. To investigate the effect of these borders on the mobility, we have evaluated the characteristics of TFTs with borders in the channel region as shown

Fig. 4. Dependency of mobility on the number of shots

in Figure 5. Figure 6 shows the TFT characteristics with and without borders. The presence of a border in the channel did not cause a decrease in mobility. However, the average mobility increased by approximately 18 %, suggesting that the

formation of rectangular grains, as depicted in Figure 3, reduced the number of grain boundaries in the same direction as that of the border in the channel, resulting in an increase in mobility. The formation of rectangular grains could be attributed to the fact that the positioning of the stage was off by approximately  $\pm 0.5~\mu m$ . This problem would be solved by using a motorized stage with sufficiently high positioning accuracy compared to the grain size.

Fig. 5. (a) Channel in single scan region, and (b) channel include borders of the single scan and double scan region.

Fig. 6. mobility of TFTs with and without border in the channel.

### 4. Conclusions

In this study, we demonstrate the feasibility of obtaining a uniform grain size in the single scan and double scan regions using ELA, by controlling the grain size and position using periodic intensity distribution. In addition, the mobility value was found to be approximately  $100 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  because the grain size was 2  $\mu$ m.

The feasibility of realizing uniform and high-mobility TFTs by applying folded irradiation to the entire surface of large glass substrates above G10 is presented. This would enable ELA on glass substrates larger than G10, which is difficult to achieve because of the difficulty in forming the line beam.

However, it is challenging to increase the mobility at the laser boundary during multi-scan annealing. To address this issue, it is necessary to evaluate the unevenness of luminance using a more statistical display with industrial lines because the positioning accuracy of the stage is insufficient, and the number of data is not sufficiently large in this study.

### References

- 1. Kim, M., Jin, G., Kim, K.B., Song, J.: Effects of the single and double (overlap) scanned excimer laser annealing on solid phase crystallized silicon films. Displays. (2015). https://doi.org/10.1016/j.displa.2014.11.001

- 2. Jin, G.H., Kim, M.: Characteristics of excimer laser-Annealed thin-Film transistors on the polycrystalline silicon morphology formed in the single and double (overlap) scanned area. Jpn. J. Appl. Phys. (2010). https://doi.org/10.1143/JJAP.49.041301

- 3. Choi, S.M., Kang, C.K., Chung, S.W., Kim, M.J., Kim, M.H., Kim, K.N., Kim, B.H.: 53.3: Redundant pixel line insertion for laser crystallization based large size LTPS AMOLED displays. In: 48th Annual SID Symposium, Seminar, and Exhibition 2010, Display Week 2010 (2010)

- 4. Fogarassy, E., De Unamuno, S., Legagneux, P., Plais, F., Pribat, D., Godard, B., Stehle, M.: Surface melt dynamics and super lateral growth

- regime in long pulse duration excimer laser crystallization of amorphous Si films. Thin Solid Films. (1999). https://doi.org/10.1016/S0040-6090(98)01434-5

- 5. Moschou, D.C., Exarchos, M.A., Kouvatsos, D.N., Papaioannou, G.J., Voutsas, A.T.: Performance and reliability of SLS ELA polysilicon TFTs fabricated with novel crystallization techniques. Microelectron. Reliab. (2007). https://doi.org/10.1016/j.microrel.2007.07.073

- Van Der Wilt, P.C., Van Dijk, B.D., Bertens, G.J., Ishihara, R., Beenakker, C.I.M.: Formation of location-controlled crystalline islands using substrate-embedded seeds in excimer-laser crystallization of silicon films. Appl. Phys. Lett. (2001). https://doi.org/10.1063/1.1402641

- 7. Mizutani, A., Hamano, F., Katayama, K., Nakamura, D., Goto, T., Ikenoue, H.: Estimation of the mobility of low temperature polycrystalline silicon thin film transistors through deep learning. Presented at the Proc. SPIE 11673, Laser Applications in Microelectronic and Optoelectronic Manufacturing (LAMOM) XXVI, 1167306 (2021). https://doi.org/10.1117/12.2579492

- 8. Chen, B.W., Chang, T.C., Chang, K.C., Hung, Y.J., Huang, S.P., Chen, H.M., Liao, P.Y., Lin, Y.H., Huang, H.C., Chiang, H.C., Yang, C.I., Zheng, Y.Z., Chu, A.K., Li, H.W., Tsai, C.H., Lu, H.H., Wang, T.T.J., Chang, T.C.: Surface Engineering of Polycrystalline Silicon for Long-Term Mechanical Stress Endurance Enhancement in Flexible Low-Temperature Poly-Si Thin-Film Transistors. ACS Appl. Mater. Interfaces. (2017). https://doi.org/10.1021/acsami.6b14525

- 9. Chen, H.T., Chen, Y.C., Lin, J.X., Hsieh, S.I., King, Y.C.: Roughness effect on uniformity and reliability of sequential lateral solidified low-temperature polycrystalline silicon thin-film transistor. Electrochem. Solid-State Lett. (2006). https://doi.org/10.1149/1.2209430

- 10. Seto, J.Y.W.: The electrical properties of polycrystalline silicon films. J. Appl. Phys. 46, 5247–5254 (1975). https://doi.org/10.1063/1.321593